SR latch

An SR latch (Set-Reset latch) is a basic digital electronic circuit that serves as a simple memory element, capable of storing a single bit of data (0 or 1). It’s a type of bistable multivibrator, meaning it has two stable states and can "latch" or hold its output until explicitly changed. The SR latch is a foundational building block in sequential logic and is often used to construct more complex circuits, like the D flip-flop we discussed earlier. Let’s dive into its details.

What It Is

- Definition: An SR latch has two inputs—S (Set) and R (Reset)—and two outputs—Q (the stored value) and Q̅ (its complement). It "sets" Q to 1 when S is activated or "resets" Q to 0 when R is activated, holding the state when neither is active.

- Purpose: Provides a way to store a bit without a clock, making it simpler than a flip-flop but less synchronized.

Main Parts of an SR Latch

- S Input (Set)

- When activated (S = 1), forces Q = 1 (sets the latch).

- Represents the "write 1" command.

- R Input (Reset)

- When activated (R = 1), forces Q = 0 (resets the latch).

- Represents the "write 0" command.

- Q Output

- The stored state of the latch (0 or 1).

- Reflects the last set or reset action.

- Q̅ Output (Q-bar)

- The inverse of Q (if Q = 1, Q̅ = 0; if Q = 0, Q̅ = 1).

- Ensures complementary outputs, useful for circuit design.

- Feedback Mechanism

- The outputs (Q and Q̅) are fed back to the inputs via logic gates, maintaining the state when S and R are inactive.

How It Works

- Implementation: Typically built with two cross-coupled NOR or NAND gates.

- NOR Gate SR Latch (simpler to explain):

- Two NOR gates, each with one input from S or R and one from the other gate’s output.

- Circuit:

- Gate 1: S + Q̅ → Q

- Gate 2: R + Q → Q̅

Truth Table (NOR SR Latch)

| S | R | Q (Next) | Q̅ (Next) | State |

|---|---|---|---|---|

| 0 | 0 | Q | Q̅ | Hold (no change) |

| 0 | 1 | 0 | 1 | Reset |

| 1 | 0 | 1 | 0 | Set |

| 1 | 1 | 0 | 0 | Invalid |

- States:

- Hold: S = 0, R = 0 → Q stays as it was (memory).

- Set: S = 1, R = 0 → Q = 1, Q̅ = 0.

- Reset: S = 0, R = 1 → Q = 0, Q̅ = 1.

- Invalid: S = 1, R = 1 → Both outputs forced to 0 (not allowed in NOR latch, as Q and Q̅ should be complements).

Demonstration

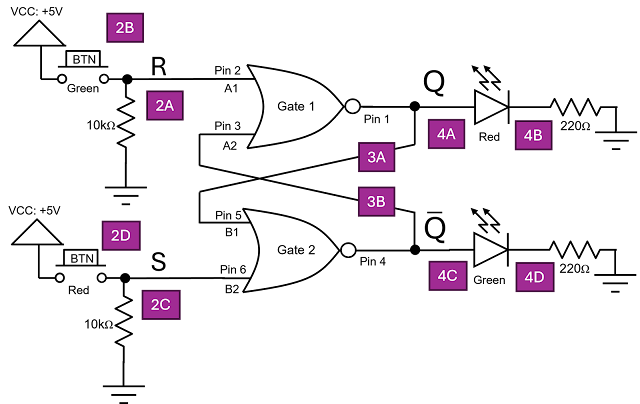

To demonstrate the workings of an SR latch using the 74LS02 chip, buttons, and LEDs, we’ll use this IC because it contains NOR gates, which are ideal for building an SR latch. We’ll design a circuit to showcase the latch’s set, reset, and hold behavior. Below, I’ll explain the setup, the SR latch’s functionality, and provide a step-by-step guide.

Chip Used: 74LS02

- Description: The 74LS02 is a TTL IC with four 2-input NOR gates.

- Pinout:

- Pin 2 (A1) & Pin 3 (B1) → Pin 1 (Y1) for the first NOR gate.

- Pin 5 (A2) & Pin 6 (B2) → Pin 4 (Y2) for the second NOR gate.

- Pin 14: VCC (5V).

- Pin 7: GND (0V).

- Why Chosen: An SR latch requires two NOR gates with cross-coupled outputs, and the 74LS02 provides these conveniently.

SR Latch Functionality

An SR latch (Set-Reset latch) is a basic memory circuit with two stable states:

- Set: Q = 1, Q̅ = 0 (when S = 1, R = 0).

- Reset: Q = 0, Q̅ = 1 (when S = 0, R = 1).

- Hold: Q retains its previous state (when S = 0, R = 0).

- Invalid: S = 1, R = 1 (not allowed, as Q and Q̅ should be complementary).

Truth Table (NOR-based SR Latch):

| S | R | Q (Next) | Q̅ (Next) | State |

|---|---|---|---|---|

| 0 | 0 | Q | Q̅ | Hold |

| 0 | 1 | 0 | 1 | Reset |

| 1 | 0 | 1 | 0 | Set |

| 1 | 1 | 0 | 0 | Invalid |

Demonstration Setup

We’ll use two NOR gates from the 74LS02 to build an SR latch, with buttons to control S and R inputs and LEDs to display Q and Q̅ outputs.

Materials Needed

- 74LS02 IC (quad 2-input NOR gate).

- Breadboard.

- Power supply: 5V DC (e.g., USB or battery with regulator).

- Two push buttons (momentary switches).

- Two LEDs (e.g., red for Q, green for Q̅).

- Resistors:

- Two 220Ω or 330Ω (for LEDs, current-limiting).

- Two 10kΩ (pull-down resistors for inputs).

- Jumper wires.

Circuit Design

We’ll use the first two NOR gates (pins 1-6):

- Gate 1 (pins 2, 3 → 1): Outputs Q.

- Gate 2 (pins 5, 6 → 4): Outputs Q̅.

- Cross-couple: Q (Pin 1) feeds to an input of Gate 2 (Pin 5), Q̅ (Pin 4) feeds to an input of Gate 1 (Pin 3).

- Power the Chip:

- Pin 14 (VCC) to +5V.

- Pin 7 (GND) to ground (0V).

- Set Up Inputs with Buttons:

- R (Reset, Pin 2):

- Connect a 10kΩ resistor from Pin 2 to ground (pull-down, LOW when not pressed).

- Connect a push button from Pin 2 to +5V (HIGH when pressed).

- S (Set, Pin 6):

- Connect a 10kΩ resistor from Pin 6 to ground (pull-down, LOW when not pressed).

- Connect a push button from Pin 6 to +5V (HIGH when pressed).

- R (Reset, Pin 2):

- Cross-Couple the Gates:

- Connect Pin 1 (Q, output of Gate 1) to Pin 5 (input A2 of Gate 2).

- Connect Pin 4 (Q̅, output of Gate 2) to Pin 3 (input B1 of Gate 1).

- Set Up Outputs with LEDs:

- Q (Pin 1):

- Connect Pin 1 to the anode of the first LED (e.g., red).

- Connect the cathode to ground via a 220Ω resistor.

- Q̅ (Pin 4):

- Connect Pin 4 to the anode of the second LED (e.g., green).

- Connect the cathode to ground via a 220Ω resistor.

- Q (Pin 1):

- Unused Gates:

- Tie unused inputs (pins 8, 9, 11, 12) to ground or VCC to prevent floating states.

How to Demonstrate

- Power On: Apply 5V. The initial state of Q and Q̅ depends on startup conditions (could be either Q = 1 or Q = 0).

- Test States:

- Hold (S = 0, R = 0):

- No buttons pressed.

- LEDs retain their previous state (e.g., Red ON, Green OFF or vice versa).

- Set (S = 1, R = 0):

- Press Button S, release Button R (if pressed).

- Red LED (Q) ON, Green LED (Q̅) OFF.

- Release Button S → LEDs hold this state (Red ON, Green OFF).

- Reset (S = 0, R = 1):

- Press Button R, release Button S (if pressed).

- Red LED (Q) OFF, Green LED (Q̅) ON.

- Release Button R → LEDs hold this state (Red OFF, Green ON).

- Invalid (S = 1, R = 1):

- Press both buttons.

- Both LEDs OFF (Q = 0, Q̅ = 0, an invalid state for an SR latch).

- Release one button → Latch settles to set or reset based on which is released first.

- Hold (S = 0, R = 0):

- Repeat: Toggle between set and reset, observing how the latch "remembers” its state when both buttons are released.

Observation:

- Red LED (Q) lights when set (S = 1), stays lit after release if R = 0.

- Green LED (Q̅) lights when reset (R = 1), stays lit after release if S = 0.