Computer Memory

Having worked on the register and the bus, I figure the next step must be to look at the memory. I asked Grok to tell me about memories in a computer. Here is the (curated) answer:

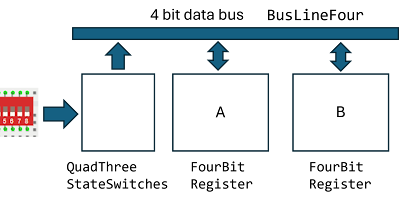

Memories in a computer are the storage systems that hold data, instructions, and intermediate results needed for processing. They come in various types, each with a specific role, speed, and capacity, working together to keep the computer running smoothly. Since you’ve been exploring registers (like your 4-bit D flip-flop setup) and buses, understanding memory ties it all together—registers are the fastest memory, while other types scale up in size and slow down in speed. Let’s dive into the details.

Types of Computer Memory

Memory is organized in a hierarchy based on speed, cost, and proximity to the CPU:

1. Registers

- What: Tiny, ultra-fast storage inside the CPU, built from flip-flops (e.g., your 4-bit register).

- Size: A few bytes.

- Speed: Nanoseconds (same as CPU clock).

- Use: Holds data being processed right now.

- Example: Your 4-bit register stores 0000–1111, updated on a clock edge.

2. Cache

- What: Small, fast memory between registers and main memory, often SRAM (Static RAM).

- Size: Kilobytes to megabytes (e.g., 32 KB in early PCs, 8 MB in modern CPUs).

- Speed: A few nanoseconds (faster than RAM, slower than registers).

- Use: Stores frequently used data/instructions to reduce main memory access.

- Note: Came later with 80286 and beyond.

3. Main Memory (RAM)

- What: Primary storage for active programs and data, typically DRAM (Dynamic RAM).

- Size: Megabytes to gigabytes (e.g., 64 KB in 8085, 16 GB in modern PCs).

- Speed: Tens of nanoseconds (e.g., ~50 ns access time).

- Use: Holds the operating system, applications, and data not currently in registers/cache.

- Volatility: Loses data when power’s off.

4. Secondary Storage

- What: Larger, slower, non-volatile storage (e.g., HDDs, SSDs).

- Size: Gigabytes to terabytes (e.g., 1 TB SSD).

- Speed: Milliseconds (HDD) to microseconds (SSD)—way slower than RAM.

- Use: Long-term storage for files, programs not currently running.

- Note: External to the CPU, accessed via I/O controllers, not directly tied to the bus like RAM.

5. ROM (Read-Only Memory)

- What: Non-volatile memory for firmware or boot code (e.g., BIOS in PCs).

- Size: Kilobytes.

- Speed: Similar to RAM (~50 ns).

- Use: Stores permanent instructions.

- Types: PROM, EPROM, EEPROM (programmable variants).

How Memory Works Together

- Hierarchy: Data moves from slow, large storage (HDD/SSD) to fast, small storage (registers) as needed.

- Bus Connection:

- Address Bus: CPU specifies memory location.

- Data Bus: Transfers data (e.g., 4 bits in your setup).

- Control Bus: Signals read (RD̅) or write (WR̅).

- Tri-State Role: Memory chips (like RAM) have tri-state outputs to drive the data bus only when selected, avoiding conflicts with registers or other devices.

Memory Technologies

SRAM (Static RAM)

- How: Uses flip-flops (like your D flip-flops) per bit—6 transistors.

- Pros: Fast, stable (no refresh needed).

- Cons: Expensive, large (fewer bits per chip).

- Use: Cache, registers.

DRAM (Dynamic RAM)

- How: Uses 1 transistor + 1 capacitor per bit—stores charge.

- Pros: Cheap, dense (more bits per chip).

- Cons: Slower, needs periodic refresh (capacitors leak).

- Use: Main memory (e.g., 8085’s 64 KB RAM).

ROM Variants

- PROM: Programmable once (fuses blown).

- EPROM: Erasable with UV light (e.g., 2716, 2 KB).

- EEPROM: Electrically erasable (modern flash precursor).

Breadboard Idea

Build a tiny memory system:

- Register: Your setup.

- RAM: 7489 SRAM (16x4):

- Connect Q0–Q3 to RAM data in/out via the bus.

- Use switches for 4-bit address (A0–A3).

- Button for write (WR̅), read via bus to 74HC4511.

- Test: Store 0101 at address 0000, read it back—display shows "5".

Building SRAM

"How can I design the 7489 myself using gates and flip-flops?":

This is my visualization of 7489:

Each empty cell holds a 0 or a 1. It is 16 x 4 as it has 16 locations (or addresses) and 4 bits per location (64 bits in total).

-cont:

7489 Overview

- Capacity: 16 words, 4 bits each (64 bits total).

- Inputs:

- 4-bit address (A0–A3) to select 1 of 16 locations.

- 4-bit data input (D0–D3) for writing.

- Outputs: 4-bit data output (Q0–Q3).

- Goal: Store 4 bits at any of 16 addresses.

Design Components

- Storage: 16 rows of 4-bit D latches (64 latches total).

- Address Decoder: Converts 4-bit address to 16 enable lines (1-of-16 selector).

- Control Logic: Gates to manage when RAM is to store data.

1. Storage (16x4 D Latches)

- Latch Choice: Use 74LS75 (quad D latch, 4 latches per IC, active-low enable).

-tbc-

Two things that I noted: We need 64 "D latches", which is new to me. Also, I do not know what an "address decoder" is.

D latch

After checking with Grok, a D latch is not the same as any of the two D flip-flops we have looked at so far (one ungated, one gated). Instead, it is basically a gated SR latch. We looked at gated SR latches in entry 14, and concluded that there are two types: a NAND version and a NOR version. This is the gated SR latch, NAND version:

It is just like a regular SR latch, with a "gate" L. When L = 1 (gate open), it is a regular SR latch, while it ignores Set and Reset when L = 0.

To make this into a D latch, we simply connect D to Set and D, through an inverter, to Reset:

- If L = 1 (gate open) and D = 1, then S = 1 and R = 0 and Q becomes 1.

- If L = 1 (gate open) and D = 0, then S = 0 and R = 1 and Q becomes 0.

- If L = 0 (gate closed) then Q will not change, no matter the value of D.

Note that the D latch does not have a clock signal. If L = 1 then Q updates immediately to the value D. I designed the component and named it DLatch according to the schedule above. This is the symbol I will use for it:

Here is the truth table for a D latch:

Address decoder

Not sure about the "Address Decoder". If I understand this correctly, we have four bits on the address bus, e.g. 0011 (or 3), coming into the decoder. Going out from the decoder will be 16 lines (numbered 0 to 15), and precisely one will be high. If the address is 0011, the decoder will make pin 3 high, and the rest low.

I need to investigate this further,... in entry 17.